Digital Controller for Power Supply Applications - Analog Devices PDF

Preview Digital Controller for Power Supply Applications - Analog Devices

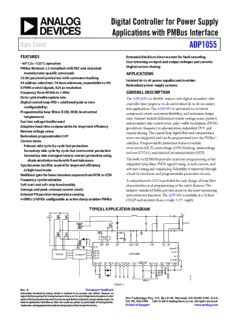

Digital Controller for Power Supply Applications with PMBus Interface Data Sheet ADP1055 FEATURES Extended black box data recorder for fault recording User trimming on input and output voltages and currents −40°C to +125°C operation Digital current sharing PMBus Revision 1.2 compliant with PEC and extended manufacturer specific commands APPLICATIONS 32-bit password protection with command masking Isolated dc-to-dc power supplies and modules 64 address selections (16 base addresses, expandable to 64) Redundant power supply systems 6 PWM control signals, 625 ps resolution Frequency from 48 kHz to 1 MHz GENERAL DESCRIPTION Duty cycle double update rate The ADP1055 is a flexible, feature-rich digital secondary side Digital control loop (PID + additional pole or zero controller that targets ac-to-dc and isolated dc-to-dc secondary configurability) side applications. The ADP1055 is optimized for minimal Programmable loop filters (CCM, DCM, low/normal component count, maximum flexibility, and minimum design temperature) time. Features include differential remote voltage sense, primary Fast line voltage feedforward and secondary side current sense, pulse-width modulation (PWM) Adaptive dead time compensation for improved efficiency generation, frequency synchronization, redundant OVP, and Remote voltage sense current sharing. The control loop digital filter and compensation Redundant programmable OVP terms are integrated and can be programmed over the PMBus™ Current sense interface. Programmable protection features include Primary side cycle-by-cycle fast protection overcurrent (OCP), overvoltage (OVP) limiting, undervoltage Secondary side cycle-by-cycle fast overcurrent protection lockout (UVLO), and external overtemperature (OTP). Secondary side averaged reverse current protection using diode emulation mode with fixed debounce The built-in EEPROM provides extensive programming of the Synchronous rectifier control for improved efficiency integrated loop filter, PWM signal timing, inrush current, and in light load mode soft start timing and sequencing. Reliability is improved through Nonlinear gain for faster transient response from DCM to CCM a built-in checksum and programmable protection circuits. Frequency synchronization A comprehensive GUI is provided for easy design of loop filter Soft start and soft stop functionality characteristics and programming of the safety features. The Average and peak constant current mode industry-standard PMBus provides access to the many monitoring External PN junction temperature sensing and system test functions. The ADP1055 is available in a 32-lead 4 GPIOs (2 GPIOs configurable as active clamp snubber PWMs) LFCSP and operates from a single 3.3 V supply. TYPICAL APPLICATION DIAGRAM DC VOUT INPUT LOAD DRIVER SR1 SR2 VFF CS2–CS2+ OVP VS+VS– CS1 ISHARE OUTA DRIVER iCoupler® OOUUTTBC ADP1055 SYNNCC OUTD VCORE RESADD JTD JRTNGPIO1TO GPIO4 CTRL SMBALRT SDASCL VDD AGNDDGND VDD PMBus 12004-001 Figure 1. Rev. A Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tel: 781.329.4700 ©2014–2015 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. Technical Support www.analog.com ADP1055 Data Sheet TABLE OF CONTENTS Features .............................................................................................. 1 Matched Cycle-by-Cycle Current Limit (OCP Equalization) ... 25 Applications ....................................................................................... 1 Low Temperature Filter ............................................................. 25 General Description ......................................................................... 1 Voltage Loop Autocorrection ................................................... 25 Typical Application Diagram .......................................................... 1 Nonlinear Gain/Response ......................................................... 26 Revision History ............................................................................... 3 Integrator Windup and Output Voltage Regulation Loss Functional Block Diagram .............................................................. 4 (Overshoot Protection) ............................................................. 26 Specifications ..................................................................................... 5 Accurate Secondary Overcurrent Protection ......................... 26 Absolute Maximum Ratings .......................................................... 10 Secondary Fast Overcurrent Protection .................................. 27 Thermal Resistance .................................................................... 10 Secondary Fast Reverse Current Protection ............................... 27 Soldering ...................................................................................... 10 Feedforward and Input Voltage Sense ..................................... 27 ESD Caution ................................................................................ 10 Accurate Overvoltage and Undervoltage Protection ............. 28 Pin Configuration and Function Descriptions ........................... 11 Fast Overvoltage Protection ...................................................... 28 Typical Performance Characteristics ........................................... 13 External Frequency Synchronization ...................................... 28 Controller Architecture ................................................................. 16 Temperature Sensing ................................................................. 29 Start-Up and Power-Down Sequencing ...................................... 17 GPIO and PGOOD Signals ....................................................... 29 VDD and VCORE Pins .............................................................. 17 GPIO3 and GPIO4 as Snubber PWM Outputs ...................... 31 Power-Up and Power-Down Commands ............................... 17 Average Constant Current Mode ............................................. 32 Power Sequencing ...................................................................... 17 32-Bit Key Code ......................................................................... 32 Power-Up and Soft Start Routine ............................................. 17 SR Phase-In, SR Transition, and SR Fast Phase-In ................ 33 Soft Stop Routine ........................................................................ 17 Output Voltage Slew Rate .......................................................... 33 VDD/VCORE OVLO ................................................................ 18 Adaptive Dead Time Compensation ....................................... 33 Control Loop and PWM Operation............................................. 19 SR Delay ....................................................................................... 34 Voltage Sense, Feedback, and Control Loop ............................. 19 Current Sharing (ISHARE Pin) ................................................ 34 Output Voltage Sense ................................................................. 19 Droop Sharing ............................................................................ 36 Digital Filter ................................................................................ 19 Light Load Mode and Deep Light Load Mode ....................... 37 Digital Filter Programming Registers ...................................... 20 Pulse Skipping ............................................................................. 37 Digital Compensation Filters During Soft Start ..................... 20 Soft Stop ....................................................................................... 37 Filter Transition .......................................................................... 20 Duty Cycle Double Update Rate .............................................. 37 Duty Balance, Volt-Second Balance, and Flux Balancing ..... 38 PWM and Synchronous Rectifier Outputs (OUTA, OUTB, OUTC, OUTD, SR1, SR2) ......................................................... 21 Fault Responses and State Machine Mechanics ......................... 39 Synchronous Rectification ........................................................ 21 Priority of Faults ......................................................................... 39 Modulation Limit ....................................................................... 22 Flags ............................................................................................. 39 Switching Frequency Programming ........................................ 22 First Fault ID (FFID) ................................................................. 39 ADCs and Telemetry ...................................................................... 23 Fault Condition During Soft Start and Soft Stop ................... 40 ADCs for Current Sensing ........................................................ 23 Watchdog Timer ......................................................................... 40 ADCs for Voltage Sensing ......................................................... 24 Standard PMBus Flags ............................................................... 42 ADCs for Temperature Sensing ................................................ 24 Black Box Feature ........................................................................... 43 Theory of Operation ...................................................................... 25 Black Box Operation .................................................................. 43 Accurate Primary Overcurrent Protection ............................... 25 Black Box Contents .................................................................... 43 Primary Fast Overcurrent Protection ...................................... 25 Black Box Timing ....................................................................... 44 Rev. A | Page 2 of 140 Data Sheet ADP1055 Black Box Readback .................................................................... 45 VDD Pin ....................................................................................... 53 Black Box Power Sequencing ..................................................... 45 SDA and SCL Pins ...................................................................... 53 Power Supply Calibration and Trim ............................................. 46 CS1 Pin ......................................................................................... 53 Voltage Calibration and Trim .................................................... 46 Exposed Pad................................................................................. 53 CS1 Trim ...................................................................................... 46 VCORE Pin .................................................................................. 53 VFF Calibration and Trim ......................................................... 46 RES Pin ......................................................................................... 53 PMBus Digital Communication .................................................... 47 JTD and JRTN Pins ..................................................................... 53 Features ......................................................................................... 47 OVP Pin ....................................................................................... 53 Overview ...................................................................................... 47 SYNC Pin ..................................................................................... 53 Transfer Protocol ......................................................................... 47 AGND and DGND ..................................................................... 53 Data Transfer Commands .......................................................... 48 EEPROM .......................................................................................... 54 Group Command Protocol ........................................................ 49 Overview ...................................................................................... 54 Clock Generation and Stretching .............................................. 49 Page Erase Operation ................................................................. 54 Start and Stop Conditions .......................................................... 49 Read Operation (Byte Read and Block Read) ......................... 54 Repeated Start Condition ........................................................... 49 Write Operation (Byte Write and Block Write) ...................... 55 General Call Support .................................................................. 49 EEPROM Password .................................................................... 55 Alert Response Address (ARA) ................................................. 49 Downloading EEPROM Settings to Internal Registers ......... 56 PMBus Address Selection .......................................................... 50 Saving Register Settings to the EEPROM ................................ 56 Fast Mode ..................................................................................... 50 EEPROM CRC Checksum ......................................................... 56 10-Bit Addressing ........................................................................ 50 Software GUI ................................................................................... 57 Packet Error Checking................................................................ 50 Standard PMBus Commands Supported by the ADP1055 ....... 58 Electrical Specifications .............................................................. 50 Manufacturer Specific Commands ............................................... 60 Fault Conditions .......................................................................... 50 Standard PMBus Command Descriptions .................................. 62 Timeout Conditions ................................................................... 51 Standard PMBus Commands .................................................... 62 Data Transmission Faults ........................................................... 51 Manufacturer Specific PMBus Command Descriptions ........... 86 Data Content Faults .................................................................... 52 Supported Switching Frequencies ............................................... 126 Layout Guidelines............................................................................ 53 Outline Dimensions ...................................................................... 140 CS2+ and CS2− Pins ................................................................... 53 Ordering Guide ......................................................................... 140 VS+ and VS− Pins ....................................................................... 53 REVISION HISTORY 3/15—Rev. 0 to Rev. A Changes to Table 1 ............................................................................ 7 Changes to Snubber Configuration Section ................................ 31 Change to Debounce Bit, Table 159 .............................................. 93 Changes to Supported Switching Frequencies Section ............126 3/14—Revision 0: Initial Version Rev. A | Page 3 of 140 ADP1055 Data Sheet FUNCTIONAL BLOCK DIAGRAM S2– S2+ S+ S– VP CS1 VFF C C V V O ADP1055 + – DAC VDD UVLO ADC ADC ADC ADC LDO CS1 OCP1 VFF CS2 OCP2 IREV VFB OVP VCORE ISHARE OUTA METERING OUTB DIGITAL DIGITAL CORE OUTC PWM COMPENSATOR ENGINE OUTD 8kB EEPROM STATE SR1 MACHINE SR2 I2C GPIO1 INTERFACE TO SYNC GPIO4 ADC ADC REF DGND SDA SCL SMBALRT ADD JTDJRTN AGND CTRL RES 12004-002 Figure 2. Functional Block Diagram (Simplified Internal Structure) Rev. A | Page 4 of 140 Data Sheet ADP1055 SPECIFICATIONS V = 3.0 V to 3.6 V, T = −40°C to +125°C, unless otherwise noted. FSR = full-scale range. DD A Table 1. Parameter Symbol Test Conditions/Comments Min Typ Max Unit SUPPLY Supply Voltage V 4.7 μF capacitor connected to AGND 3.0 3.3 3.6 V DD Supply Current I Normal operation (CTRL pin is high) 63 mA DD Normal operation (CTRL pin is low) 55 mA During EEPROM programming (40 ms) I + 8 mA DD During black box write I + 8 mA DD Current with VDD < VCORE POR 100 μA POWER-ON RESET Power-On Reset POR V rising 3.0 V DD Undervoltage Lockout UVLO V falling 2.75 2.85 2.97 V DD Overvoltage Lockout OVLO 3.8 4.0 4.1 V OVLO Debounce Set to 2 μs (Register 0xFE4D[5] = 0) 2.0 μs Set to 500 μs (Register 0xFE4D[5] = 1) 500 μs VCORE PIN 0.33 μF capacitor connected to DGND Power-On Reset (POR) V falling 2.1 V DD Output Voltage T = 25°C 2.6 V A Maximum Time from POR to No black box recording 10 ms Outputs Switching (Register 0xFE48[1:0] = 00) With black box recording 45 ms (Register 0xFE48[1:0] = 01, 10, or 11) OSCILLATOR AND PLL PLL Frequency RES = 10 kΩ (±0.1%) 190 200 210 MHz OUTA, OUTB, OUTC, OUTD, SR1, SR2 PINS Output Low Voltage V Sink current = 10 mA 0.8 V OL Output High Voltage V Source current = 10 mA V − 0.8 V OH DD Rise Time C = 50 pF 3.5 ns LOAD Fall Time C = 50 pF 1.5 ns LOAD VOLTAGE FEEDFORWARD (VFF PIN) ADC Clock Frequency 1.56 MHz Feedforward (Slow) Input V For reporting; equivalent resolution 0 1 1.6 V FF Voltage Range of 12 bits ADC Usable Input Voltage Range 0 1.57 V Measurement Accuracy (Slow Factory trimmed at 1.0 V and Fast Feedforward) 0% to 100% of usable input voltage range −2.5 +2.5 % FSR 10% to 90% of usable input voltage range −2.0 +2.0 % FSR 900 mV to 1.1 V −1.5 +1.5 % FSR Leakage Current 1.0 μA FEEDFORWARD FUNCTION (VFF PIN) Feedforward (Fast) Input 0.6 1 1.6 V Voltage Range Sampling Period for Equivalent resolution of 12 bits 1 μs Feedforward (Fast) ADC VS LOW SPEED ADC Input Voltage Range Differential voltage from VS+ to VS− 0 1 1.6 V Usable Input Voltage Range 0 1.55 V ADC Clock Frequency 1.56 MHz Rev. A | Page 5 of 140 ADP1055 Data Sheet Parameter Symbol Test Conditions/Comments Min Typ Max Unit ADC Update Rate Registers are updated at this rate, 10.5 ms equivalent resolution of 12 bits Measurement Accuracy Factory trimmed at 1.0 V 0% to 100% of usable input voltage range −2.75 +2.75 % FSR 10% to 90% of usable input voltage range −2.0 +2.0 % FSR 900 mV to 1.1 V −1.75 +1.75 % FSR Temperature Coefficient V = 3.3 V, VS± = 1.0 V 110 ppm/°C DD Leakage Current 1.0 μA Common-Mode Voltage Offset Maximum voltage differential from VS− −0.25 +0.25 % FSR Error to AGND of ±200 mV VS OVP DIGITAL COMPARATOR VS OVP Accuracy −2.0 +2.0 % FSR VS OVP Comparator Speed Register 0xFE4D[3:2] = 00, equivalent 82 μs resolution of 7 bits VS UVP DIGITAL COMPARATOR VS UVP Accuracy −2.0 +2.0 % FSR Propagation Delay Does not include debounce time 80 μs (Register 0xFE30[13:11] = 00) VS HIGH SPEED ADC Sampling Frequency 10 MHz Equivalent Resolution 6 Bits Dynamic Range ±50 mV FAST OVP COMPARATOR (OVP PIN) Threshold Accuracy Factory trimmed at 1.206 V −1.2 0 +1.5 % Other thresholds (0.8 V to 1.6 V) −2.0 +2.0 % Propagation Delay (Latency) Register 0xFE2F[1:0] = 00 40 80 ns CURRENT SENSE 1 (CS1 PIN) Input Voltage Range V 0 1 1.6 V IN Usable Input Voltage Range 0 1.56 V ADC Clock Frequency 1.56 MHz Update Rate Registers are updated at this rate, 10.5 ms equivalent resolution of 12 bits Current Sense Measurement Factory trimmed at 1.0 V; tested under dc Accuracy input conditions 10% to 60% of usable input voltage range −1.5 +1.5 % FSR 10% to 90% of usable input voltage range −2.0 +2.0 % FSR 0% to 100% of usable input voltage range −2.5 +2.5 % FSR Current Sense Measurement 12 Bits CS1 Fast OCP Threshold Register 0xFE2C[2] = 0 1.17 1.2 1.23 V Register 0xFE2C[2] = 1 242 250 258 mV CS1 Fast OCP Speed 40 80 ns CS1 Accurate OCP Speed 10.5 ms Leakage Current 1.5 μA CURRENT SENSE 2 (CS2+, CS2− PINS) Current Sense Measurement For updating registers (constant current 12 Bits Resolution mode enabled or disabled) ADC Clock Frequency 1.56 MHz 30 mV Range1 Register 0xFE4F[1:0] = 00 0 30 mV Usable Input Range 0 21 mV 60 mV Range1 Register 0xFE4F[1:0] = 01 0 60 mV Usable Input Range 0 45 mV 480 mV Range1 Register 0xFE4F[1] = 10 0 480 mV Usable Input Range 0 414 mV Rev. A | Page 6 of 140 Data Sheet ADP1055 Parameter Symbol Test Conditions/Comments Min Typ Max Unit Temperature Coefficient V = 3.3 V DD 30 mV Range 0 mV to 19 mV 326 ppm/°C 0 mV to 21 mV 354 ppm/°C 60 mV Range 0 mV to 41 mV 172 ppm/°C 0 mV to 45 mV 194 ppm/°C 480 mV Range 0 mV to 374 mV 83 ppm/°C 0 mV to 414 mV 84 ppm/°C CURRENT SENSE MEASUREMENT ACCURACY (CS2+, CS2− PINS) 30 mV Setting 0 mV to 19 mV −2.9 +2.9 % FSR 0 mV to 21 mV −3.1 +3.1 % FSR 60 mV Setting 0 mV to 41 mV −1.9 +1.9 % FSR 0 mV to 45 mV −2.1 +2.1 % FSR 480 mV Setting 0 mV to 374 mV −1.5 +1.5 % FSR 0 mV to 414 mV −1.7 +1.7 % FSR Internal Level Shifting Current All ranges 25 μA CS2 Accurate OCP Speed 2.6 ms COMMON-MODE VOLTAGE OFFSET Maximum voltage differential from CS2− ERROR (CS2+, CS2− PINS) to AGND of ±50 mV 30 mV Range −1.0 +1.0 % FSR 60 mV Range −0.5 +0.5 % FSR 480 mV Range −0.25 +0.25 % FSR CS2 OCP FAST COMPARATORS For CS2 fast OCP and peak constant (CS2+, CS2− PINS) current mode CS2 Forward Comparator Accuracy Range of 0 mV to 60 mV Threshold set at 0 mV −10.3 % FSR Threshold set at 15.24 mV −10.1 % FSR Threshold set at 30.48 mV −23.8 +16.7 % FSR Threshold set at 45.71 mV −10.2 % FSR Threshold set at 60 mV −10.2 % FSR Range of 0 mV to 600 mV Threshold set at 0 mV −0.8 % FSR Threshold set at 152.4 mV 0.1 % FSR Threshold set at 304.8 mV −7.1 +7.6 % FSR Threshold set at 457.1 mV 0.9 % FSR Threshold set at 600 mV 1.3 % FSR Reverse Comparator Accuracy Range of 0 mV to 30 mV Threshold set at 0 mV −11.8 % FSR Threshold set at 7.62 mV −11.8 % FSR Threshold set at 15.24 mV −13.8 +16.9 % FSR Threshold set at 22.86 mV 12.7 % FSR Threshold set at 30 mV 12.5 % FSR Range of −30 mV to 0 mV Threshold set at 0 mV 17.1 % FSR Threshold set at −7.62 mV 16.9 % FSR Threshold set at −15.24 mV −9.5 +23.2 % FSR Threshold set at −22.86 mV 17.6 % FSR Threshold set at −30 mV 17.4 % FSR Propagation Delay Register 0xFE2D[1:0] = 00 (diode 40 80 ns emulation mode) JTD TEMPERATURE SENSE ADC Clock Frequency 1.56 MHz Update Rate For updating registers (14-bit resolution) Reverse Sensing Enabled 200 ms Reverse Sensing Disabled 130 ms Rev. A | Page 7 of 140 ADP1055 Data Sheet Parameter Symbol Test Conditions/Comments Min Typ Max Unit Measurement Accuracy for With BC847A transistor (n = 1.00); f External Temperature Sensor Register 0xFE5A[2:0] = 0x04 Forward Temperature Sensor Error from −40°C to +25°C −11.7 +13.4 °C Error from 25°C to 125°C −8.9 +14.7 °C Reverse Temperature Sensor Error from 25°C to 125°C −9.7 +14.4 °C CTRL, SMBALRT, SYNC, GPIO1 TO Digital inputs/outputs GPIO4, ISHARE PINS Input Low Voltage V 0.8 V IL Input High Voltage V V − 0.8 V IH DD Propagation Delay 40 ns GPIOx Rise Time GPIOx configured as an output 3.5 ns GPIOx Fall Time GPIOx configured as an output 1.5 ns Leakage Current SMBALRT, SYNC, GPIO1 TO GPIO4, and 1.0 μA ISHARE pins CTRLpin 10.0 μA SYNC PIN Synchronization to external frequency 50 1000 kHz Minimum On Pulse 40 ns Synchronization Range2 −10.0 +10.0 % f SW Leakage Current 1.0 μA BLACK BOX PROGRAMMING TIME 1.2 36 × 1.2 ms SDA/SCL PINS Input Low Voltage V 0.8 V IL Input High Voltage V 2.1 V IH Output Low Voltage V 0.4 V OL Leakage Current 1.0 μA SERIAL BUS TIMING See Figure 3 Clock Operating Frequency 10 100 400 kHz Bus Free Time t Between stop and start conditions 1.3 μs BUF Start Hold Time t Hold time after (repeated) start condition; 0.6 μs HD;STA after this period, the first clock is generated Start Setup Time t Repeated start condition setup time 0.6 μs SU;STA Stop Setup Time t 0.6 μs SU;STO SDA Setup Time t 100 ns SU;DAT SDA Hold Time t For write and for readback 300 ns HD;DAT SCL Low Timeout t 25 35 ms TIMEOUT SCL Low Period t 1.3 μs LOW SCL High Period t 0.6 μs HIGH Clock Low Extend Time t 25 ms LO;SEXT SCL, SDA Fall Time t 20 300 ns F SCL, SDA Rise Time t 20 300 ns R EEPROM RELIABILITY Endurance3 T = 85°C 10,000 Cycles J T = 125°C 1000 Cycles J Data Retention4 T = 85°C 20 Years J T = 125°C 15 Years J 1 Differential voltage from CS2+ to CS2−. 2 fSW is the switching frequency set in Register 0x33. 3 Endurance is qualified as per JEDEC Standard 22, Method A117, and is measured at −40°C, +25°C, +85°C, and +125°C. 4 Retention lifetime equivalent at junction temperature (TJ) = 85°C as per JEDEC Standard 22, Method A117. Retention lifetime derates with junction temperature. Rev. A | Page 8 of 140 Data Sheet ADP1055 t t R F tLOW tHD;STA SCL tHD;STA tHD;DAT tHIGH tSU;DAT tSU;STA tSU;STO SDA PtBUFS S P 12004-003 Figure 3. Serial Bus Timing Diagram Rev. A | Page 9 of 140 ADP1055 Data Sheet ABSOLUTE MAXIMUM RATINGS THERMAL RESISTANCE Table 2. Parameter Rating θ is specified for the worst-case conditions, that is, a device JA Supply Voltage (Continuous), VDD 4.2 V soldered in a circuit board for surface-mount packages. Digital Pins: OUTA, OUTB, OUTC, −0.3 V to VDD + 0.3 V Table 3. Thermal Resistance OUTD, SR1, SR2, GPIO1, GPIO2, GPIO3, GPIO4, SMBALRT, SYNC Package Type θJA θJC Unit VS−, AGND, DGND −0.3 V to +0.3 V 32-Lead LFCSP 44.4 6.4 °C/W VS+ −0.3 V to VDD + 0.3 V SOLDERING JTD, JRTN, ADD −0.3 V to VDD + 0.3 V It is important to follow the correct guidelines when laying out CS1, CS2+, CS2− −0.3 V to VDD + 0.3 V the PCB footprint for the ADP1055 and when soldering the SDA, SCL −0.3 V to VDD + 0.3 V device onto the PCB. For detailed information about these ISHARE −0.3 V to VDD + 0.3 V guidelines, see the AN-772 Application Note. Operating Temperature Range −40°C to +125°C Storage Temperature Range −65°C to +150°C ESD CAUTION Junction Temperature 150°C Peak Solder Reflow Temperature SnPb Assemblies 240°C (10 sec to 30 sec) RoHS-Compliant Assemblies 260°C (20 sec to 40 sec) ESD Charged Device Model 500 V Human Body Model 2.5 kV Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability. Rev. A | Page 10 of 140

Description: