ANP-40 Current Mode Compensation Techniques PDF

Preview ANP-40 Current Mode Compensation Techniques

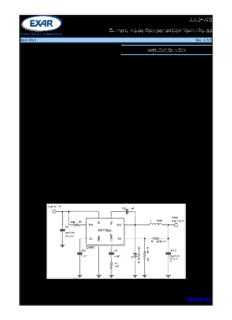

AANNPP--4400 CCuurrrreenntt MMooddee CCoommppeennssaattiioonn TTeecchhnniiqquueess April 2013 Rev. 1.0.0 0 GENERAL DESCRIP/1T3I ON AAPPPPLLIICCAATTIIOONN NNOOTTEE This application note shows an analysis of the XRP7664 gain blocks with specific information on selecting the frequency compensation FEATURES component values. A key item of note is that This application note applies to the the ESR of output capacitors creates a zero in XRP7664, XRP7665, XRP7674 and the loop response that can affect stability. The XRP7675 products application circuits shown in the datasheets (Figure 1), along with the design information Shows the internal gain blocks of the given, show a typical application using ceramic device capacitors. Ceramic capacitors have a very low Analysis the total loop including ESR so the ESR zero with ceramics is usually external components at a high enough frequency that it doesn’t adversely affect the stability. Other types of Address the effect of using large capacitors, such as aluminum and tantalum output capacitor values with large ESR types, can have notably higher ESR, which, in Gives a specific procedure for conjunction with their higher capacitance, can compensating a design using the Bode result in the ESR zero being at a low enough plot method frequency to affect the loop. Graphing templates, Figure 6 and This application note also applies to the Figure 7, for manual drawing the Bode XRP7665, XRP7674, and XRP7675 specifically plots. but can also provide understanding in compensating any current mode buck DC/DC. Figure 1: Datasheet Application Circuit Exar Corporation www.exar.com 48720 Kato Road, Fremont CA 94538, USA Tel. +1 510 668-7000 – Fax. +1 510 668-7001 AANNPP--4400 CCuurrrreenntt MMooddee CCoommppeennssaattiioonn TTeecchhnniiqquueess OVERVIEW OF THE XRP7764 Cc = Compensation Capacitor FUNCTION Co = Output Capacitor Cp = Additional Pole Capacitor INTERNAL GAIN BLOCK DIAGRAM EA = Error Amp ESR = Output Capacitor ESR VOin Vin GEA = Error Amp Gain in dB R1 IN Isen GMOD = MOD Gain in dB VRef IEAo - Lo EA + xy VO Lo = Output Inductor FB Mod SW Isw ICo Io MOD = Modulator 500k Rc = Compensation Resistor COMP R2 RLD RLD = External Load Resistance AIEA = 800 uA/V ICOMP ESR VCOMP = Error Amp Output AIMOD = 3.5 A/V Cp Rc VFB = Feedback Input Voltage Where: Co Vo = Output Voltage EA = Error Amp Mod = Modulator Cc Vref = Internal Reference Voltage QUICK COMPENSATION PROCEDURE Figure 2: Internal Gain Blocks The values required for the compensation will Figure 2 shows a diagram of the XRP7664 depend on the output filter and the selected internal gain blocks. The total loop includes cross over frequency. For most designs that the feedback divider (DIV) created by R1 and use ceramic output capacitors, the addition of R2, Error Amp (EA), Modular (MOD), and Cp across Rc will not be necessary, but if a output filter. Since the error amp is a high value of output capacitance, in transconductance amplifier its output voltage conjunction with a high ESR, is used for Co, will be a function of IEAo and the impedance the additional pole created by Cp may be from its output to ground. Please note that required for stability. In all cases bode plot this includes its internal 500kΩ (R ) LIM drawings should be made during the design impedance. and Gain/Phase measurements should be done on the final product. Additionally, since the modulator is current mode control, its output current (Isw) is The design example used here is for a proportional to in input control voltage. XRP7664. This procedure, however, also Current mode control, under most operating applies to the other devices listed in the conditions, effectively removes the effect of Features section on page 1. Be sure to use the output inductor from the filter equation the correct datasheet values for the particular and results in the output voltage (Vo) being a device. function of Isw times the output impedance from Vo to ground. Vout = 3.3V ILD Max = 2A TERMS USED Co = 1200μF ESR = 0.01Ω The following terms are used in the figures and RLIM = 500kΩ throughout this application note. The values used in AIEA = 800μA/V (From Datasheet) this document should reflect those shown in the AVEA= 400V/V (From Datasheet) datasheet. In any case where they don’t agree, the AIMOD = 3.5A/V (From Datasheet) information in the datasheet shall be deemed Fco = 10kHz correct. Vref = 0.925V AIEA = EA Transconductance Unless otherwise stated: Current is in Amps, AIMOD = MOD Transconductance Voltage is in Volts, Resistance in Ohms, AVDIV = Feedback Voltage Divider Capacitance in Farad, and Frequency in Hertz. AVEA = EA Voltage Gain AVMOD = MOD Voltage Gain © 2013 Exar Corporation 2/13 Rev. 1.0.0 AANNPP--4400 CCuurrrreenntt MMooddee CCoommppeennssaattiioonn TTeecchhnniiqquueess 1. Select the crossover frequency 3. Determine the error amp pole frequency for the Fco chosen Select the frequency where the loop gain should cross 0dB. Typically the crossover Divide Fco by the total DC gain to get the pole frequency (Fco) should be around 5% to 10% frequency that needs to be created set Fco. of the 350kHz switching frequency. For this F example we are using 10kHz. CO FP CO AVTOTdc FPCO15.444 2. Calculate the total DC gain of the loop There are three main DC gain blocks in the loop; 4. Find the Pole and Zero of the output AV , The input voltage divider made up of filter at full load. DIV R1 and R2. The gain of this block is: 1 1) Select the cross over frequency, Fco : FP AV VRef 0.28 o 2 CoRLD ESR DIV Vo FP 79.897 o AV , The Error Amp DC Gain is the gain from EA 1 the datasheet or 400V/V. FZ o 2 C ESR AV 400 o EA FZ 13.263k o AV , The Modulator gain can be calculated MOD from the modulator transconductance of 3.5 and the output load resistance at maximum 5. Compensating the design load current. Set the EA poles and the EA zero at the Vo 3.3 following frequencies. R 1.65 LD ILD 2 FPEA1FPCO AV AI R FP FZ MODdc MOD LD EA2 o AVMOD 3.51.65 5.775 FZEAFPo Now calculate the compensation component values. The total DC Gain of the loop is the sum of the three blocks. FP EA1 R R C LIM AVTOTdc AVFBAVEAAVMOD FZEAFPEA1 AVTOTdc 0.34005.775 647.5 RC 120k 1 C c The total gain in dB is. 2 FZEARC GTOTdc 20log AVTOTdc Cc 16.6n GTOTdc 56.2 RC RLIM C P 2 FPEA2RCRLIM C 124p P © 2013 Exar Corporation 3/13 Rev. 1.0.0 AANNPP--4400 CCuurrrreenntt MMooddee CCoommppeennssaattiioonn TTeecchhnniiqquueess 6. Creating a Bode Gain/Phase plot and gains for each pole and zero at that frequency. Once this is done connect all the Gathering together the key parameters gives. points with straight lines. Component Values This is the gain versus frequency response for Cc = 16nF the total loop. Rc = 120k Cp = 100pF Plotting the Phase, Figure 5 Compensation Data On the phase graph, at each pole and zero G = 57dB frequency, put a point on the graph as TOTdc follows. FPo = 80Hz If the frequency is a pole put a point at that FZo = 13.3kHz frequency at -45 degrees. FP = 14Hz EA1 Then draw a line that starts at 0 degrees, one FP = 13.3kHz decade below the pole frequency, goes EA2 through the -45 degree point, and ends at - FZ = 80Hz EA 90 degrees one decade above the pole frequency. 7. Do a Bode Gain/Phase plot to ensure stability Now complete the plot for that pole by drawing a horizontal line from the -90 This can be done either manually using semi- degrees point to the end of the graph on the log graph paper, or automatically using a right and from the 0 degree point to the end Bode plot tool. of the graph on the left. Figure 4 and Figure 5, show Gain and Phase If the frequency is a zero put a point at that plots of the example given. These were drawn frequency at +45 degrees. manually to show the technique as shown below. Then draw a line that starts at 0 degrees, one decade below the pole frequency, goes through the +45 degree point, and ends at +90 degrees one decade above the pole Plotting Manually the Gain, Figure 4 frequency. On the gain graph draw a horizontal line at 57 Now complete the plot for that zero by dB from 1Hz to 100kHz to represent the DC drawing a horizontal line from the +90 gain. degrees point to the end of the graph on the Move left to right along the 0 dB line until you right and from the 0 degree point to the end reach a pole or zero frequency and put a of the graph at the left. point on the 0dB line at that frequency. Repeat the above for every pole and zero. If the frequency is pole, draw a line from that Once this is done identify each frequency point toward the right that decrease with a where a pole’s or zero’s phase reaches 0, -90 slope of -20dB per decade and if the and +90 degrees. Then at each of these frequency is a zero, draw a line from that frequencies add up all the phase values and point toward the right that increases with a put a point on the graph. slope of -20dB per decade. The phase margin for the full loop can now be Continue until all poles and zeros have been plotted by drawing straight lines between drawn. these points. Now put points at each pole and zero frequency that equal the sum of the DC gain © 2013 Exar Corporation 4/13 Rev. 1.0.0 AANNPP--4400 CCuurrrreenntt MMooddee CCoommppeennssaattiioonn TTeecchhnniiqquueess Stability Criteria add +180 degree. For example if the phase value at FCO was -120 degrees then the loop There two main stability criteria for a stable phase margin would be 180 + (-120) = 60 power supply loop. One is Gain Margin and degrees. the other is Phase Margin. The gain margin is defined as the gain of the Simulation Circuit loop at the frequency above FCO that the Below is a circuit that can be used to plot the phase crosses -180 degrees. Look at phase Gain/Phase using a spice type simulator. plot to see if the phase goes below -180 degrees. If it does look at that frequency on RLIM the gain plot to make sure that the loop has R1 EA MOD negative gain. The gain should be at least FB SW LO below -10 dB and preferably below -20 dB. G = AIEA G = AIMOD The phase margin is defined at the FCO COMP ESR frequency where the gain crosses 0 dB. The V RLD R2 phase margin is the difference between the AC CP RC CO loop phase and -180 degrees at this frequency. CC For a robust design the phase margin should be at least 45 degrees. A simple way to check Figure 3: Simulation Model this is to take the loop phase value at FCO and © 2013 Exar Corporation 5/13 Rev. 1.0.0 AANNPP--4400 CCuurrrreenntt MMooddee CCoommppeennssaattiioonn TTeecchhnniiqquueess GAIN/PHASE PLOTS OF THE EXAMPLE DESIGN Gain vs Freq 60 40 20 0 Line )B DC Gain d ( nia0 FPEA1 G Fpo Fzo -20 FPEA2 FZEA Total -40 -60 1 10 100 Frequency (Hz) 1000 10000 100000 Figure 4: Gain Plots of Example Phase vs. Freq 180 135 90 0 Line 45 )s FPEA1 e e rge0 Fpo D ( e Fzo s a h P-45 FPEA2 FZEA -90 Total -135 -180 1 10 100 1000 10000 100000 Frequency Figure 5: Phase Plots of Example © 2013 Exar Corporation 6/13 Rev. 1.0.0 AANNPP--4400 CCuurrrreenntt MMooddee CCoommppeennssaattiioonn TTeecchhnniiqquueess GRAPHING PAPER Gain vs Freq 60 40 20 )B d ( nia0 G -20 -40 -60 1 10 100 Frequency (Hz) 1000 10000 100000 Figure 6: Gain Graphing Paper Phase vs. Freq 180 135 90 45 )s e e rge 0 D ( e s a hP-45 -90 -135 -180 1 10 100 Frequency 1000 10000 100000 Figure 7: Phase Graphing Paper © 2013 Exar Corporation 7/13 Rev. 1.0.0 AANNPP--4400 CCuurrrreenntt MMooddee CCoommppeennssaattiioonn TTeecchhnniiqquueess APPENDIX DETAILED FREQUENCY ANALYSIS The following is a detailed analysis of the loop gain. The analysis is applicable to all the XRP devices listed in the Feature section on page 1. VOin Vin R1 IN Isen VRef IEAo - Lo EA + xy VO SW FB Mod Isw ICo Io 500k COMP R2 RLD AIEA = 800 uA/V ICOMP ESR AIMOD = 3.5 A/V Rc Where: Co EA = Error Amp Mod = Modulator Cc Fig. A1: Circuit Diagram Where: AIEA = EA Transconductance GMOD = MOD Gain in dB AIMOD = MOD Transconductance Lo = Output Inductor AV = Feedback Voltage Divider MOD = Modulator DIV AVEA = EA Voltage Gain Rc = Compensation Resistor AVMOD = MOD Voltage Gain RLD = External Load Resistance Cc = Compensation Capacitor VCOMP = Error Amp Output Co = Output Capacitor VFB = Feedback Input Voltage EA = Error Amp Vo = Output Voltage ESR = Output Capacitor ESR Vref = Internal Reference Voltage GEA = Error Amp Gain in dB XRP7664 Internal Gain Block Diagram Figure A1 shows a diagram of the XRP7664 internal gain blocks. The total loop includes the feedback divider, Error Amp (EA), Modular (MOD), and Output filter. Since the error amp is a transconductance amplifier its output voltage will be a function of IEAo and the impedance from its output to ground. Please note that this includes its internal 500kΩ impedance. Additionally, since the modulator is current mode control, its output current (Isw) is proportional to in input control voltage. Current mode control, under most operating conditions, effectively © 2013 Exar Corporation 8/13 Rev. 1.0.0 AANNPP--4400 CCuurrrreenntt MMooddee CCoommppeennssaattiioonn TTeecchhnniiqquueess removes the effect of the output inductor from the filter equation and results in the output voltage (Vo) being a function of Isw times the output impedance from Vo to ground. Analysis of the open loop gain Tracing the voltages from the output back to the input gives: Vo I Z SW VO Eq. 1: I AI V Eq. 2: SW mod comp V I Z Eq. 3: COMP EAo EAo I AI V Eq. 4: EAo EA FB V A V Eq. 5: FB DIV Oin The Transfer Function of the total loop is: V Z AI AI Z A V O VO MOD EA EAo DIV Oin Eq. 6: The total loop gain is: V O AV Z AI AI Z A LOOP VO MOD EA EAo DIV V Oin Eq. 7: Now let’s explore the individual blocks. Modulator and Output Filter Blocks The modulator voltage gain, AVMOD, is a function of its specified transconductance and the impedance of the output filter. Since the modulator uses Current Mode Control, its output is a controlled current source. It therefore controls the current flowing in the output inductor (Lo). This effectively removes the output inductance (Lo) from loop equation. The gain of the modulator is calculated as follows: AV AI Z Eq. 8: MOD MOD VO ZVO is the parallel combination of R ||(Z +ESR) so: LD Co Z ESR Co Z R VO LD R Z ESR LD CO Eq. 9: © 2013 Exar Corporation 9/13 Rev. 1.0.0 AANNPP--4400 CCuurrrreenntt MMooddee CCoommppeennssaattiioonn TTeecchhnniiqquueess Z ESR Co AV AI R MOD MOD LD R Z ESR Eq. 10: LD CO The modulator gain can be separated into two components; DC and AC. AV AI R Eq. 11: MODdc MOD LD Z ESR sC ESR 1 Co o AV MODac R Z ESR sC R ESR 1 Eq. 12a: LD CO o LD Eq. 12b Error Amplifier Block The Error Amp is also a transconductance amplifier and its voltage gain is a function of its output impedance. AV is calculated similar to the Modulator. EA AV AI Z Eq. 13: EA EA EAo The output impedance of Z is the parallel combination of RLIM||(ZCc+RC) EAo Z R Cc C Z R EAo LIM R Z R Eq. 14: LIM Cc C Z R Cc C AV AI R EA MOD LIM R Z R LIM Cc C Eq. 15: The error amp gain can also be separated into DC and AC components. AV AI R Eq. 16 EAdc EA LIM Z R sC R 1 Cc C C c AV EAac R Z R sC R R 1 LIM Cc C c LIM C Eq. 17a: Eq. 17b Feedback Divider Block The final gain block in the loop is the feedback voltage divider which sets the output voltage by dropping the output voltage down to the error amp reference voltage level. Since there are no reactive components in the divider, the gain of this block is DC with no AC component: V R2 Ref A DIVdc R1 R2 V O Eq. 18a: Eq. 18b © 2013 Exar Corporation 10/13 Rev. 1.0.0

Description: