ALM-GP001 PDF

Preview ALM-GP001

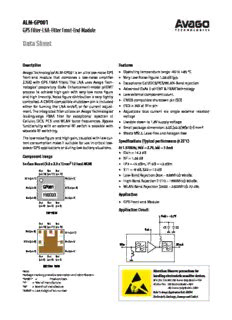

ALM-GP001 GPS Filter-LNA-Filter Front-End Module Data Sheet Description Features Avago Technologies’ ALM-GP001 is an ultra low-noise GPS • Operating temperature range -40 to +85 °C front-end module that combines a low-noise amplifier • Very Low Noise Figure: 1.26 dB typ. (LNA) with GPS FBAR filters. The LNA uses Avago Tech- • Exceptional Cell/DCS/PCS/WLAN-Band rejection nologies’ proprietary GaAs Enhancement-mode pHEMT • Advanced GaAs E-pHEMT & FBAR Technology process to achieve high gain with very low noise figure • Low external component count. and high linearity. Noise figure distribution is very tightly • CMOS compatible shutdown pin (SD) controlled. A CMOS-compatible shutdown pin is included either for turning the LNA on/off, or for current adjust- • ESD: > 3kV at RFin pin ment. The integrated filter utilizes an Avago Technologies’ • Adjustable bias current via single external resistor/ leading-edge FBAR filter for exceptional rejection at voltage Cellular, DCS, PCS and WLAN band frequencies. Bypass • Useable down to 1.8V supply voltage functionality with an external RF switch is possible with • Small package dimension: 3.0(L)x2.5(W)x1(H) mm3 separate RF switching. • Meets MSL3, Lead-free and halogen free The low noise figure and high gain, coupled with low cur- Specifications (Typical performance @ 25°C) rent consumption make it suitable for use in critical low- power GPS applications or during low-battery situations. At 1.575GHz, Vdd = 2.7V, Idd = 7.5mA • Gain = 14.2 dB Component Image • NF = 1.26 dB Surface Mount (3.0 x 2.5 x 1) mm3 12-lead MCOB • IIP3 = +5 dBm, IP1dB = +2 dBm • S11 = -9 dB, S22 =-12 dB Gnd Vsd Gnd (pin 12) (pin 11) (pin 10) • Low-Band Rejection (824 – 928MHz): 89 dBc RF In (pin 1) Vdd (pin 9) • High-Band Rejection (1710 – 1980MHz): 80 dBc GP001 • WLAN-Band Rejection (2400 – 2500MHz): 72 dBc Gnd (pin 2) RF Out (pin 8) YMXXXX Application Gnd (pin 3) Gnd (pin 7) Gnd Gnd Gnd • GPS Front-end Module (pin 4) (pin 5) (pin 6) Application Circuit TOP VIEW Vdd = +2.7V Gnd Vsd Gnd (pin 10) (pin 11) (pin 12) C1 C2 Vsd Vdd (pin 9) RF In (pin 1) RF Out (pin 8) Gnd (pin 2) RFin RFout Gnd (pin 7) Gnd (pin 3) Gnd Gnd Gnd (pin 6) (pin 5) (pin 4) BOTTOM VIEW Note: Attention: Observe precautions for Package marking provides orientation and identification handling electrostatic sensitive devices. “GP001” = Product Code RF In (Pin 1) to GND: ESD Human Body Model = 3 kV “Y” = Year of manufacture All other Pins : ESD Machine Model = 50 V “M” = Month of manufacture : ESD Human Body Model = 300 V “XXXX” = Last 4 digit of lot number Refer to Avago Application Note A004R: Electrostatic Discharge, Damage and Control. Absolute Maximum Rating[1] T =25°C A Absolute Thermal Resistance [3] Symbol Parameter Units Max. (Vdd = 2.7V, Idd = 7.5mA), θjc = 92°C/W Vdd Device Drain to Source Voltage[2] V 3.6 Notes: 1. Operation of this device in excess of any of Idd Drain Current[2] mA 20 these limits may cause permanent damage. Pin,max CW RF Input Power (Vdd = 2.7V, Idd = 7.5mA) dBm 15 2. Assuming DC quiescent conditions. 3. Thermal resistance measured using Infra-Red Pdiss Total Power Dissipation[4] mW 72 measurement technique. Tj Junction Temperature °C 150 4. Board (module belly) temperature TB is 25°C. Derate 10.87 mW/°C for TB>143°C. TSTG Storage Temperature °C -65 to 150 Electrical Specifications TA = 25°C, Freq = 1.575GHz, measured on demo board[1] unless otherwise specified – Typical Performance[1] Table 1. Performance at Vdd = Vsd = 2.7V, Idd = 7.5mA (Rbias = 6.8k Ohm) nominal operating conditions Symbol Parameter and Test Condition Units Min. Typ Max. G Gain dB 12 14.2 16.3 NF[2] Noise Figure dB – 1.26 1.7 IP1dB Input 1dB Compressed Power dBm – +2 – IIP3[3] Input 3rd Order Intercept Point (2-tone @ Fc +/- 2.5MHz) dBm 0 +5 – S11 Input Return Loss dB – -9 – S22 Output Return Loss dB – -12 – S12 Reverse Isolation dB – -22 – Low Band Rejection Worst-case relative to 1.575GHz within dBc 79 89 – (827-928)MHz band, tested at 928MHz High Band Rejection Worst-case relative to 1.575GHz within dBc 74 80 – (1710-1980)MHz band, tested at 1850MHz WLAN Band Rejection Worst-case relative to 1.575GHz within dBc 67 72 – (2400-2500)MHz band, tested at 2500MHz IP1dB890MHz Input 1dB gain compression interferer signal level at dBm – 21 – 890MHz IP1dB1710MHz Input 1dB gain compression interferer signal level at dBm – 32 – 1710MHz IP1dB1885MHz Input 1dB gain compression interferer signal level at dBm – 37 – 1885MHz IP1dB2500MHz Input 1dB gain compression interferer signal level at dBm – 35 - 2500MHz OOB IIP3[4] Out of Band Input 3rd Order Intercept Point dBm – 62 – (2-tone @ 1712.7 MHz and 1850MHz) Idd Supply DC current at Shutdown (SD) voltage Vsd = 2.7V mA 4 7.5 15 Ish Shutdown Current @ VSD = 0V uA – 0.5 110 2 Table 2. Performance at Vdd = Vsd = 1.8V, Idd = 5mA (Rbias = 2.7k Ohm) nominal operating conditions Symbol Parameter and Test Condition Units Typ G Gain dB 12.8 NF[2] Noise Figure dB 1.35 IP1dB Input 1dB Compressed Power dBm 0 IIP3[3] Input 3rd Order Intercept Point (2-tone @ Fc +/- 2.5MHz) dBm 3.5 S11 Input Return Loss dB -8 S22 Output Return Loss dB -11.5 S12 Reverse Isolation dB -21 Low Band Rejection Worst-case relative to 1.575GHz within (827-928)MHz band, dBc 89 tested at 928MHz High Band Rejection Worst-case relative to 1.575GHz within (1710-1980)MHz band, dBc 79 tested at 1850MHz WLAN Band Rejection Worst-case relative to 1.575GHz within (2400-2500)MHz band, dBc 71 tested at 2500MHz IP1dB890MHz Input 1dB gain compression interferer signal level at 890MHz dBm 20 IP1dB1710MHz Input 1dB gain compression interferer signal level at 1710MHz dBm 32 IP1dB1885MHz Input 1dB gain compression interferer signal level at 1885MHz dBm 37 IP1dB2500MHz Input 1dB gain compression interferer signal level at 2500MHz dBm 35 Idd Supply DC current at Shutdown (SD) voltage Vsd = 1.8V mA 5 Notes: 1. Measurements at 1.575GHz obtained using demo board 2. Losses from demoboard deembeded 3. 1.575GHz IIP3 test condition: FRF1 = 1572.5 MHz, FRF2 = 1577.5 MHz with input power of -20dBm per tone measured at the worst case side band 4. 1.575GHz IIP3 test condition: FRF1 = 1712.7 MHz, FRF2 = 1850 MHz with input power of 10dBm per tone measured at the worst case side band 3 4 3 2 1 GND SD VDD GND C1 R1 L1 C3 R2 C2 RFOUT GP001 YMXXXX SN2-B1 Avago Tech Sep 2009 DC Pin Configuration of 4-Pins connector Pins Pins 1, 4 = GND 1 2 3 4 pointing out Pin 2 = Vdd Supply of the page Pin 3 = Shutdown (SD) Circuit Symbol Size Description L1 0402 22 nH Inductor (Taiyo Yuden HK100522NJ-T) C1 0805 0.1 uF Capacitor (Murata GRM21BR71H104KA01L) C2 0402 47 pF Capacitor (Kyocera CM05CH470J50AHF) C3 0402 6.8 pF Capacitor (Kyocera CM05CG6R8C50AHF) R1 0402 12 Ohms Resistor (RK73B1ETTP120J) R2 0402 6.8 kohm Resistor (RK73B1ETTP6R8J) Figure 1. Demoboard and application circuit components table 4 Vdd=+2.7V C1 0.1uF R1* L1* Vsd C3* C2 R2* 47pF Vdd RFin RFout Figure 2. Application Circuit * optional, see notes below Notes: • The ALM-GP001 can be operated with supply voltage (Vdd) from 1.5V to 2.85V. Vsd can operate from 1V to Vdd. • The module is fully matched at the input and output RF pins. The RFinput pin is connected directly to a shunt inductor to ground. As such a DC blocking capacitor is required if DC voltages are present. The RFoutput pin is already DC-blocked by the internal filter inside the module. • Best noise performance is obtained using high-Q wirewound inductors. This circuit demonstrates that low noise figures are obtainable with standard 0402 chip inductors. • C1 and C2 are bypass capacitors for RF and low frequency stability and linearity . • L1 and R1 isolates the demoboard from external disturbances during measurement. It is not needed in actual application. Likewise, C3 mitigate the effect of external noise pickup on the Vsd line. This component are not required in actual operation. Minimal component operation is as shown in the schematic on page 1. • Bias control is achieved by either varying the Vsd voltage with/ without R2, or fixing the Vsd voltage to Vdd and adjusting R2 for the desired current. 5 ALM-GP001 Typical Performance Curves at 25° 20 5 20 5 0 0 0 0 -20 -5 R -20 -5 R Gain (dB)--6400 Low band High bandWLAN band --1150 eturn loss (dB Gain (dB) --6400 --1150 eturn loss (dB ) ) Gain (dB) Gain (dB) -80 Input RL (dB) -20 -80 Input RL (dB) -20 Output RL (dB) Output RL (dB) -100 -25 -100 -25 0.0 0.4 0.8 1.2 1.6 2.0 2.4 2.8 3.2 3.6 4.0 1.50 1.52 1.54 1.56 1.58 1.60 1.62 Freq (GHz) Freq (GHz) Figure 3a. Typical S-Parameter Plot @ Vdd = 2.7V, Idd = 7.5mA Figure 3b. Passband response of typical S-Parameter Plot @ Vdd = 2.7V, Idd = 7.5mA -65 -65 -70 B) B) 1 (d -75 1 (d -70 2 2 S S -80 -85 -75 0.8 0.9 1.7 1.8 1.9 2.0 Freq (GHz) Freq (GHz) Figure 3c. Rejection plot for Low band @ Vdd = 2.7V, Idd = 7.5mA Figure 3d. Rejection plot for High band @ Vdd = 2.7V, Idd = 7.5mA -57 -58 B) d 1 ( 2 S -59 -60 2.4 2.5 Freq (GHz) Figure 3e. Rejection plot for WLAN band @ Vdd = 2.7V, Idd = 7.5mA 6 ALM-GP001 Typical Performance Curves at 25° 20 5 20 5 0 0 0 0 -20 -5 R -20 -5 R e e n (dB)-40 -10turn lo n (dB)-40 -10turn lo Gai-60 -15ss (dB Gai-60 -15ss (dB ) ) Gain (dB) Gain (dB) -80 Input RL (dB) -20 -80 Input RL (dB) -20 Output RL (dB) Output RL (dB) -100 -25 -100 -25 0.0 0.4 0.8 1.2 1.6 2.0 2.4 2.8 3.2 3.6 4.0 1.50 1.52 1.54 1.56 1.58 1.60 1.62 1.64 Freq (GHz) Freq (GHz) Figure 4a. Typical S-Parameter Plot @ Vdd = 1.8V, Idd = 5mA Figure 4b. Passband response of typical S-Parameter Plot @ Vdd = 1.8V, Idd = 5mA 14 13 12 Vdd=2.7v 12 Vdd=1.8v 11 10 10 9 8 mA) 8 mA)7 Idd ( 6 Idd (56 4 4 3 2 2 1 0 0 0 5 10 15 20 25 30 35 40 45 50 55 60 0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 Rbias (kohm) Vsd (V) Figure 5. Idd vs Rbias at 25°C Figure 6. Idd vs Vsd for Vdd = 2.7V, R2 = 6.8k Ohm 9 8 7 6 A) 5 m d ( 4 d I 3 2 1 0 0 0.5 1 1.5 2 2.5 3 Vsd (V) Figure 7. Idd vs Vsd for Vdd = 1.8V, R2 = 2.7k Ohm 7 ALM-GP001 Typical Performance Curves 2.6 2.6 -40°C -40°C 2.4 2.4 25°C 25°C 2.2 85°C 2.2 85°C dB)2.0 dB)2.0 RE (1.8 RE (1.8 U U G G FI1.6 FI1.6 E E S S OI1.4 OI1.4 N N 1.2 1.2 1.0 1.0 0.8 0.8 2 4 6 8 10 12 14 16 0 2 4 6 8 10 Idd (mA) Idd (mA) Figure 8. NF vs. Idd at Vdd = 2.7V Figure 9. NF vs Idd at Vdd = 1.8V 16 16 15 15 14 14 B) 13 B) 13 d d N ( N ( AI 12 AI 12 G G 11 11 -40°C -40°C 25°C 25°C 10 10 85°C 85°C 9 9 2 4 6 8 10 12 14 16 0 2 4 6 8 10 Idd (mA) Idd (mA) Figure 10. Gain vs. Idd at Vdd = 2.7V Figure 11. Gain vs. Idd at Vdd = 1.8V -65 -65 -40°C -40°C -70 25°C -70 25°C 85°C Bc) 85°C dBc) -75 N (d -75 ON ( CTIO CTI -80 EJE -80 E R EJ D W R -85 AN -85 LO W B O -90 L -90 -95 -95 2 4 6 8 10 12 14 16 0 2 4 6 8 10 Idd (mA) Idd (mA) Figure 12. Low band rejection vs. Idd at Vdd = 2.7V Figure 13. Low band rejection vs. Idd at Vdd = 1.8V 8 ALM-GP001 Typical Performance Curves -65 -65 -40°C -40°C -70 25°C -70 25°C Bc) 85°C Bc) 85°C d d N (-75 N (-75 O O REJECTI-80 REJECTI-80 D D AN-85 AN-85 B B PCS -90 PCS -90 -95 -95 2 4 6 8 10 12 14 16 0 2 4 6 8 10 Idd (mA) Idd (mA) Figure 14. High band rejection vs. Idd at Vdd = 2.7V Figure 15. High band rejection vs. Idd at Vdd = 1.8V -65 -65 -70 -70 Bc) Bc) d d N (-75 N (-75 O O REJECTI-80 REJECTI-80 D D N N A-85 A-85 B B AN -40°C AN -40°C WL-90 25°C WL-90 25°C 85°C 85°C -95 -95 2 4 6 8 10 12 14 16 18 0 2 4 6 8 10 Idd (mA) Idd (mA) Figure 16. WLAN band rejection vs. Idd at Vdd = 2.7V Figure 17. WLAN band rejection vs. Idd at Vdd = 1.8V 5 12 4mA 4 10 6mA 8mA 3 10mA 8 Bm) 2 m) d B dB ( 1 3 (d6 1 P IP II4 0 4mA 6mA -1 8mA 2 10mA -2 0 1.8 2.0 2.2 2.4 2.6 2.8 3.0 3.2 3.4 1.8 2.0 2.2 2.4 2.6 2.8 3.0 3.2 3.4 Vdd (V) Vdd (V) Figure 18. IP1dB vs. Vdd at 25°C Figure 19. IIP3 vs. Vdd at 25°C 9 ALM-GP001 Typical Performance Curves at 25° 2.0 2.0 1.8 1.8 111 eee 111 mmm MuMuMu1.6 PriPriPri1.6 u..u..u.. MuMuMu _M_M_M1.4 u..u..u..1.4 CCC MMM _25deg_40deg_85deg1.2 5degC_0degC_5degC_1.2 248 1.0 ___1.0 0.8 0.8 0 2 4 6 8 10 12 14 16 18 20 0 2 4 6 8 10 12 14 16 18 20 freq, GHz freq, GHz Figure 20. Edwards-Sinsky Output Stability Factor (Mu) at Vdd = 2.7V Figure 21. Edwards-Sinsky Input Stability Factor (Mu’) at Vdd = 2.7V 2.0 2.0 1.8 e1e1e11.8 111 mmm Mu..MuMu..MuMu..Mu1.6 MuPriMuPriMuPri1.6 8v_8v_8v_1.4 Mu..Mu..Mu..1.4 _25degC_1p_40degC_1p_85degC_1p11..02 degC_1p8v_degC_1p8v_degC_1p8v_11..02 505 248 ___ 0.8 0.8 0 2 4 6 8 10 12 14 16 18 20 0 2 4 6 8 10 12 14 16 18 20 freq, GHz freq, GHz Figure 22. Edwards-Sinsky Output Stability Factor (Mu) at Vdd = 1.8V Figure 23. Edwards-Sinsky Input Stability Factor (Mu’) at Vdd = 1.8V 10

Description: